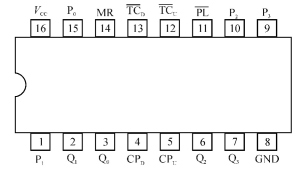

74ls192引脚图及功能表

74ls192是一款高速CMOS四位同步计数器芯片,也被称为BCD decade up/down counter。它可以实现二进制加法和减法操作,并且输出结果可以采用BCD码表示。下面我们来详细介绍74ls192的引脚图及功能表。

引脚图

引脚功能

- CP(时钟输入)端口:时钟输入端口,当CP端口接收到一个上升沿时,计数器会在下一个时钟周期内进行计数。

- P(数据输入)端口:数据输入端口,用于设置初始值或者进行加减运算。

- T(计数方向控制)端口:计数方向控制端口,当T端口为高电平时,计数器进行加法操作,否则进行减法操作。

- PE(使能输入)端口:使能输入端口,当PE端口为低电平时,计数器处于禁止状态。

- MR(清零输入)端口:清零输入端口,当MR端口为低电平时,计数器清零。

- QA~QD(数据输出)端口:四个数据输出端口,用于输出计数器的当前值。

- RC(复位时钟输入)端口:复位时钟输入端口,当RC端口接收到一个上升沿时,计数器将被重置。

功能表

下面是74ls192芯片的功能表:

| T | CP | PE | MR | 操作 |

|---|---|---|---|---|

| X | ↑ | ↑ | ↑ | 无操作 |

| X | ↑ | ↑ | ↓ | 计数器不工作 |

| X | ↓ | X | X | 保持原状态 |

| 0 | ↑ | 0 | X | 计数器减1 |

| 1 | ↑ | 0 | X | 计数器加1 |

| X | ↑ | 1 | X | 保持原状态 |

| X | ↑ | X | 0 | 计数器清零 |

| X | ↑ | X | 1 | 保持原状态 |

74ls192芯片工作原理

74ls192芯片是一种高速CMOS电路集成块。它采用四位同步计数器的结构,可以实现二进制加法和减法运算,并且输出结果可以采用BCD码表示。当CP端口接收到一个上升沿时,计数器会在下一个时钟周期内进行计数。T端口用于控制计数方向,PE端口用于控制计数器的使能状态,MR端口用于清零计数器,QA~QD端口用于输出计数器的当前值。

在74ls192芯片中,当T端口为高电平时,计数器将进行加法操作;当T端口为低电平时,计数器将进行减法操作。PE端口可以控制计数器的工作状态,当PE端口为低电平时,计数器处于禁止状态,不会进行任何计数操作。MR端口用于清零计数器,当MR端口为低电平时,计数器将被重置,并从0开始重新计数。

总之,74ls192芯片具有功能强大、使用方便等优点,在数字电路中被广泛应用。